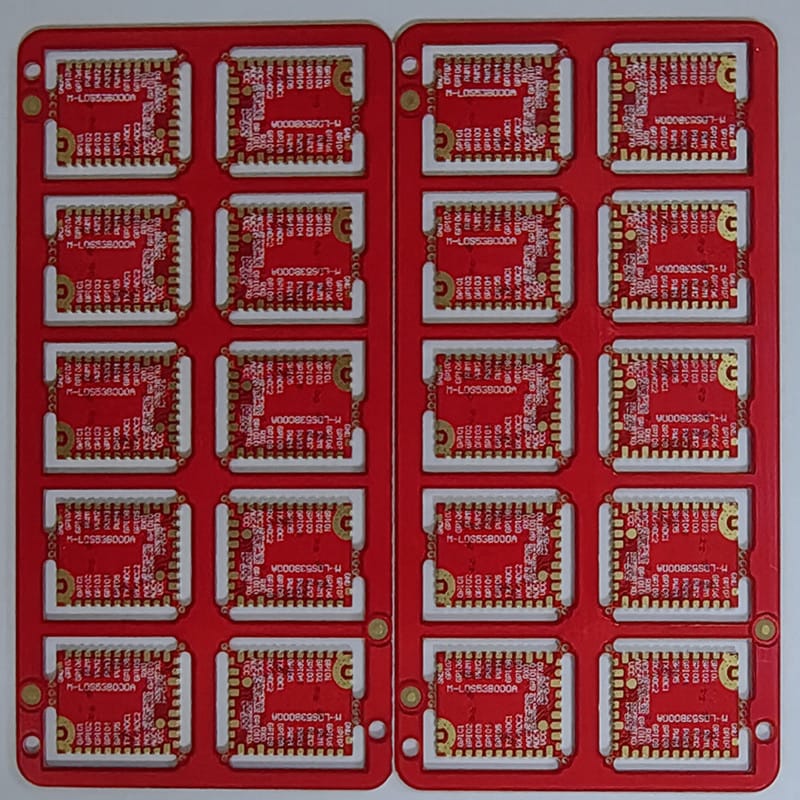

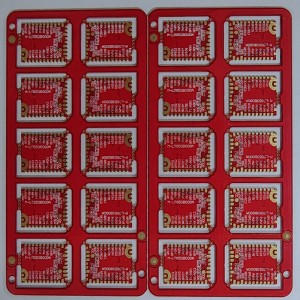

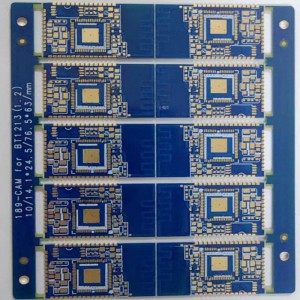

Prototyp gedréckte Leiterplatten ROUT Lötmaske Kressellächer

Produkt Spezifikatioun:

| Basismaterial: | FR4 TG140 |

| PCB-Déckt: | 1,0 +/- 10% mm |

| Zuel vun de Schichten: | 4L |

| Kupferdicke: | 1/1/1/1 oz |

| Uewerflächenbehandlung: | ENIG 2U” |

| Lötmaske: | Glanzend rout |

| Seidedrock: | Wäiss |

| Spezialprozess: | Pth Halleflächer op de Kanten |

Applikatioun

D'Prozesser vu platéierten Halleflächer sinn:

1. Veraarbecht dat halleft Säitelach mat engem duebele V-fërmegen Schnëttwierkzell.

2. Den zweete Buer füügt Führungslächer op der Säit vum Lach bäi, läscht d'Kupferhaut am Viraus, reduzéiert Graten a benotzt Nutenfräser amplaz vu Buerer fir d'Geschwindegkeet an d'Fallgeschwindegkeet ze optimiséieren.

3. Taucht Koffer an, fir de Substrat galvaniséieren, sou datt eng Schicht Koffer op der Lachwand vum ronne Lach um Rand vun der Plack galvaniséiert gëtt.

4. Produktioun vun der baussenzeger Schichtschicht nom Laminéieren, Beliichtung an Entwécklung vum Substrat hannereneen, gëtt de Substrat enger sekundärer Kupferplatéierung an enger Verzinnplatéierung ënnerworf, sou datt d'Kupferschicht op der Lachwand vum ronne Lach um Rand vun der Plack verdickt gëtt an d'Kupferschicht mat enger Zinnschicht fir Korrosiounsbeständegkeet bedeckt ass;

5. Halleflachformung Schneit dat ronnt Lach um Rand vum Brett an der Halschent fir en halleft Lach ze bilden;

6. Beim Entfernen vum Film gëtt den Anti-Galvaniséierungsfilm, deen während dem Filmpressprozess gepresst gouf, ewechgeholl;

7. D'Ätze vum Substrat gëtt geätzt, an de fräigeleeëne Koffer op der äusserer Schicht vum Substrat gëtt duerch Ätze ewechgeholl;

8. Zinnentfernung De Substrat gëtt vum Zinn entfernt, sou datt den Zinn op der Halleflachwand ewechgeholl ka ginn, an d'Kupferschicht op der Halleflachwand fräigeluecht gëtt.

9. Nom Formen, benotzt rout Klebeband fir d'Eenheetsplacken zesummenzepechen, an d'Graten duerch d'alkalesch Ätzlinn ewechzehuelen.

10. Nom zweete Kupferplattéierung an der Verzinnung um Substrat gëtt dat ronnt Lach um Rand vun der Plack an der Halschent geschnidden, fir en halleft Lach ze bilden, well d'Kupferschicht vun der Lachwand mat enger Zinnschicht bedeckt ass, an d'Kupferschicht vun der Lachwand komplett intakt mat der Kupferschicht vun der äusserer Schicht vum Substrat ass. D'Verbindung, déi eng staark Bindekraaft involvéiert, kann effektiv verhënneren, datt d'Kupferschicht op der Lachwand ofgezunn gëtt oder datt de Kupfer sech beim Schneiden verformt;

11. Nodeems d'Halleflachformung fäerdeg ass, gëtt de Film ewechgeholl an dann geätzt, sou datt d'Kupferuewerfläch net oxidéiert gëtt, wat effektiv d'Optriede vu Reschtkupfer oder souguer Kuerzschluss verhënnert, an d'Ausbezuelungsquote vun der metalliséierter Halleflach-PCB-Leiterplatte verbessert.

FAQs

E platéierten Halleflach oder Kressellach ass eng stempelfërmeg Kant, déi duerch halbéiert Schnëtt um Kontur geschnidden gëtt. E platéierten Halleflach ass eng méi héich Niveau vu platéierte Kanten fir gedréckte Leiterplatten, déi normalerweis fir Board-zu-Board Verbindungen benotzt gëtt.

E Via gëtt als Verbindung tëscht Kupferschichten op enger PCB benotzt, während de PTH normalerweis méi grouss wéi de Via gemaach ass a als platéiert Lach fir d'Akzeptanz vu Komponentleitungen benotzt gëtt - wéi z. B. net-SMT-Widerstänn, Kondensatoren an DIP-Package-IC. E PTH kann och als Lächer fir eng mechanesch Verbindung benotzt ginn, während Via dat net onbedéngt maache kann.

D'Beschichtung vun den Duerchgangslächer ass aus Koffer, engem Leeder, sou datt d'elektresch Leetfäegkeet duerch d'Plack fléisst. Net-beschichtete Duerchgangslächer hunn keng Leetfäegkeet, dofir kënnt Dir, wann Dir se benotzt, nëmmen nëtzlech Kofferschinnen op enger Säit vun der Plack hunn.

Et ginn 3 Zorte vu Lächer an enger PCB, plated through hole (PTH), unplated through hole (NPTH) a Via Holes, dës sollten net mat Slots oder Cut-outs verwiesselt ginn.

Vum IPC-Standard ass et +/- 0,08 mm fir pth an +/- 0,05 mm fir npth.